Z80

レジスタ

| 名前 | サイズ | 説明 | ||||||

|---|---|---|---|---|---|---|---|---|

| AF | 16bit |

| ||||||

| BC | 16bit |

| ||||||

| DE | 16bit |

| ||||||

| HL | 16bit |

| ||||||

| AF' | 16bit | 裏アキュムレータ・フラグレジスタ | ||||||

| BC' | 16bit | 裏汎用レジスタBC | ||||||

| DE' | 16bit | 裏汎用レジスタDE | ||||||

| HL' | 16bit | 裏汎用レジスタHL | ||||||

| IX | 16bit |

| ||||||

| IY | 16bit |

| ||||||

| SP | 16bit | スタックポインタ | ||||||

| PC | 16bit | プログラムカウンタ | ||||||

| I | 8bit | 割り込みページアドレス | ||||||

| R | 8bit | メモリリフレッシュレジスタ |

| ※1 | 未定義命令使用時のみ |

1. フラグ

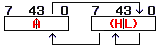

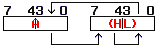

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| S | Z | - | H | - | P/V | N | C |

| S |

| ||||||||

| Z |

| ||||||||

| H |

| ||||||||

| P/V |

| ||||||||

| N |

| ||||||||

| C |

| ||||||||

| - | 未使用 ※1 |

| ※1 | 命令により変化あり |

命令一覧表

記号の説明

1. サイズ欄

| B | オペランドサイズが8ビット |

| W | オペランドサイズが16ビット |

2. ニーモニック欄

| # | 8/16ビットの即値データ |

| #3 | ビット位置(0 - 7) |

| #8 | I/Oアドレス(0x00 - 0xff)※1 |

| #16 | 絶対アドレス(0x0000 - 0xffff) |

| d | 相対アドレス(-128 - 127) |

| r | A/B/C/D/E/H/L/BC/DE/HL/SP レジスタ |

| ur | IXH/IXL/IYH/IYL レジスタ |

| cc | フラグ状態 NZ/Z/NC/C/PO/PE/P/M |

| $ | 命令が置かれている先頭アドレス |

| ※1 | アドレスバスへの出力は、命令により上位8bitにA/Bレジスタの内容が出力されるため16bit |

3. 機能欄

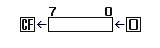

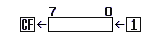

| CF | キャリーフラグ |

| [7:0] | 下位8ビット(7 - 0 ビット) |

| [15:8] | 上位8ビット(15 - 8 ビット) |

4. フラグ欄(SZXHXPNC)

| - | 変化なし |

| * | 命令の実行により変化 |

| ? | 不定 |

| 0 | 0にクリア |

| 1 | 1をセット |

| P | パリティーフラグとして変化 |

| V | オーバーフローフラグとして変化 |

| I | IFF2状態 |

| B | BC<>0時に1 |

| H | 変更前のCF |

5. ステート欄

| 1ステート | 1クロック |

命令

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| LD | B- | LD r,r | r ← r | -------- | 1 | 4 | |

| B- | LD r,# | r ← # | -------- | 2 | 7 | ||

| B- | LD ur,r | ur ← r | -------- | 2 | 8 | r = A/B/C/D/E/IXH/IXL | |

| B- | LD r,ur | r ← ur | -------- | 2 | 8 | r = A/B/C/D/E/IXH/IXL | |

| B- | LD ur,# | ur ← # | -------- | 3 | 10 | ||

| B- | LD A,(BC) | A ← (BC) | -------- | 1 | 7 | ||

| B- | LD A,(DE) | A ← (DE) | -------- | 1 | 7 | ||

| B- | LD r,(HL) | r ← (HL) | -------- | 1 | 7 | ||

| B- | LD A,(#16) | A ← (#16) | -------- | 3 | 13 | ||

| B- | LD r,(IX+d) | r ← (IX+d) | -------- | 3 | 19 | ||

| B- | LD r,(IY+d) | r ← (IY+d) | -------- | 3 | 19 | ||

| B- | LD (BC),A | (BC) ← A | -------- | 1 | 7 | ||

| B- | LD (DE),A | (DE) ← A | -------- | 1 | 7 | ||

| B- | LD (HL),r | (HL) ← r | -------- | 1 | 7 | ||

| B- | LD (HL),# | (HL) ← # | -------- | 2 | 10 | ||

| B- | LD (#16),A | (#16) ← A | -------- | 3 | 13 | ||

| B- | LD (IX+d),r | (IX+d) ← r | -------- | 3 | 19 | ||

| B- | LD (IX+d),# | (IX+d) ← # | -------- | 4 | 19 | ||

| B- | LD (IY+d),r | (IY+d) ← r | -------- | 3 | 19 | ||

| B- | LD (IY+d),# | (IY+d) ← # | -------- | 4 | 19 | ||

| -W | LD r,# | r ← # | -------- | 3 | 10 | ||

| -W | LD r,(#16) | r ← (#16) | -------- | 4 | 20 | ||

| -W | LD HL,(#16) | HL ← (#16) | -------- | 3 | 16 | ||

| -W | LD IX,(#16) | IX ← (#16) | -------- | 4 | 20 | ||

| -W | LD IY,(#16) | IY ← (#16) | -------- | 4 | 20 | ||

| -W | LD (#16),r | (#16) ← r | -------- | 4 | 20 | ||

| -W | LD (#16),HL | (#16) ← HL | -------- | 3 | 16 | ||

| -W | LD (#16),IX | (#16) ← IX | -------- | 4 | 20 | ||

| -W | LD (#16),IY | (#16) ← IY | -------- | 4 | 20 | ||

| -W | LD IX,# | IX ← # | -------- | 4 | 14 | ||

| -W | LD IY,# | IY ← # | -------- | 4 | 14 | ||

| -W | LD SP,HL | SP ← HL | -------- | 1 | 6 | ||

| -W | LD SP,IX | SP ← IX | -------- | 2 | 10 | ||

| -W | LD SP,IY | SP ← IY | -------- | 2 | 10 | ||

| B- | LD A,I | A ← I | ***0*I0- | 2 | 9 | ||

| B- | LD A,R | A ← R | ***0*I0- | 2 | 9 | ||

| B- | LD I,A | I ← A | -------- | 2 | 9 | ||

| B- | LD R,A | R ← A | -------- | 2 | 9 | ||

| PUSH | -W | PUSH rr | SP ← SP - 1 : (SP) ← rr[15:8] SP ← SP - 1 : (SP) ← rr[7:0] | -------- | 1 | 11 | rr = BC/DE/HL/AF |

| -W | PUSH IX | SP ← SP - 1 : (SP) ← IXH SP ← SP - 1 : (SP) ← IXL | -------- | 2 | 15 | ||

| -W | PUSH IY | SP ← SP - 1 : (SP) ← IYH SP ← SP - 1 : (SP) ← IYL | -------- | 2 | 15 | ||

| POP | -W | POP AF | F ← (SP) : SP ← SP + 1 A ← (SP) : SP ← SP + 1 | ******** | 1 | 10 | |

| -W | POP rr | rr[7:0] ← (SP) : SP ← SP + 1 rr[15:8] ← (SP) : SP ← SP + 1 | -------- | 1 | 10 | rr = BC/DE/HL | |

| -W | POP IX | IXL ← (SP) : SP ← SP + 1 IXH ← (SP) : SP ← SP + 1 | -------- | 2 | 14 | ||

| -W | POP IY | IYL ← (SP) : SP ← SP + 1 IYH ← (SP) : SP ← SP + 1 | -------- | 2 | 14 | ||

| LDI | B- | LDI | (DE) ← (HL) DE ← DE + 1 HL ← HL + 1 BC ← BC - 1 if BC=0 then P/V=0 else P/V=1 | --*0*B0- | 2 | 16 | |

| LDIR | B- | LDIR | do { LDI } while [BC<>0] | --*0*00- | 2 | 21 [BC<>0] 16 [BC=0] | |

| LDD | B- | LDD | (DE) ← (HL) DE ← DE - 1 HL ← HL - 1 BC ← BC - 1 if BC=0 then P/V=0 else P/V=1 | --*0*B0- | 2 | 16 | |

| LDDR | B- | LDDR | do { LDD } while [BC<>0] | --*0*00- | 2 | 21 [BC<>0] 16 [BC=0] | |

| CPI | B- | CPI | if [A-(HL)]=0 then Z ← 1 else Z ← 0 HL ← HL + 1 BC ← BC - 1 if BC=0 then P/V ← 0 else P/V ← 1 | *****B1- | 2 | 16 | |

| CPIR | B- | CPIR | do { CPI } while [Z=0 and BC<>0] | *****B1- | 2 | 21 [Z=0 and BC<>0] 16 [Z=1 or BC=0] | |

| CPD | B- | CPD | if [A-(HL)]=0 then Z ← 1 else Z ← 0 HL ← HL - 1 BC ← BC - 1 if BC=0 then P/V ← 0 else P/V ← 1 | *****B1- | 2 | 16 | |

| CPDR | B- | CPDR | do { CPD } while [Z=0 and BC<>0] | *****B1- | 2 | 21 [Z=0 and BC<>0] 16 [Z=1 or BC=0] |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| EX | -W | EX AF,AF' | AF ⇔ AF' | ******** | 1 | 4 | |

| -W | EX DE,HL | DE ⇔ HL | -------- | 1 | 4 | ||

| -W | EX (SP),HL | (SP) ⇔ HL | -------- | 1 | 19 | ||

| -W | EX (SP),IX | (SP) ⇔ IX | -------- | 2 | 23 | ||

| -W | EX (SP),IY | (SP) ⇔ IY | -------- | 2 | 23 | ||

| EXX | -W | EXX | BC ⇔ BC' DE ⇔ DE' HL ⇔ HL' | -------- | 1 | 4 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| ADD | B- | ADD A, r | A ← A + r | *****V0* | 1 | 4 | |

| B- | ADD A, ur | A ← A + ur | *****V0* | 2 | 8 | ||

| B- | ADD A, # | A ← A + # | *****V0* | 2 | 7 | ||

| B- | ADD A, (HL) | A ← A + (HL) | *****V0* | 1 | 7 | ||

| B- | ADD A, (IX+d) | A ← A + (IX+d) | *****V0* | 3 | 19 | ||

| B- | ADD A, (IY+d) | A ← A + (IY+d) | *****V0* | 3 | 19 | ||

| -W | ADD HL, r | HL ← HL + r | --*?*-0* | 1 | 11 | ||

| -W | ADD IX, rr | IX ← IX + rr | --*?*-0* | 2 | 15 | rr = BC/DE/IX/SP | |

| -W | ADD IY, rr | IY ← IY + rr | --*?*-0* | 2 | 15 | rr = BC/DE/IY/SP | |

| ADC | B- | ADC A, r | A ← A + r + CF | *****V0* | 1 | 4 | |

| B- | ADC A, ur | A ← A + ur + CF | *****V0* | 2 | 8 | ||

| B- | ADC A, # | A ← A + # + CF | *****V0* | 2 | 7 | ||

| B- | ADC A, (HL) | A ← A + (HL) + CF | *****V0* | 1 | 7 | ||

| B- | ADC A, (IX+d) | A ← A + (IX+d) + CF | *****V0* | 3 | 19 | ||

| B- | ADC A, (IY+d) | A ← A + (IY+d) + CF | *****V0* | 3 | 19 | ||

| -W | ADC HL, r | HL ← A + r + CF | ***?*V0* | 2 | 15 | ||

| SUB | B- | SUB A, r | A ← A - r | *****V1* | 1 | 4 | |

| B- | SUB A, ur | A ← A - ur | *****V1* | 2 | 8 | ||

| B- | SUB A, # | A ← A - # | *****V1* | 2 | 7 | ||

| B- | SUB A, (HL) | A ← A - (HL) | *****V1* | 1 | 7 | ||

| B- | SUB A, (IX+d) | A ← A - (IX+d) | *****V1* | 3 | 19 | ||

| B- | SUB A, (IY+d) | A ← A - (IY+d) | *****V1* | 3 | 19 | ||

| SBC | B- | SBC A, r | A ← A - r - CF | *****V1* | 1 | 4 | |

| B- | SBC A, ur | A ← A - ur - CF | *****V1* | 2 | 8 | ||

| B- | SBC A, # | A ← A - # - CF | *****V1* | 2 | 7 | ||

| B- | SBC A, (HL) | A ← A - (HL) - CF | *****V1* | 1 | 7 | ||

| B- | SBC A, (IX+d) | A ← A - (IX+d) - CF | *****V1* | 3 | 19 | ||

| B- | SBC A, (IY+d) | A ← A - (IY+d) - CF | *****V1* | 3 | 19 | ||

| -W | SBC HL, r | HL ← HL - r - CF | ***?*V1* | 2 | 15 | ||

| CP | B- | CP A, r | A - r | *****V1* | 1 | 4 | |

| B- | CP A, ur | A - ur | *****V1* | 2 | 8 | ||

| B- | CP A, # | A - # | *****V1* | 2 | 7 | ||

| B- | CP A, (HL) | A - (HL) | *****V1* | 1 | 7 | ||

| B- | CP A, (IX+d) | A - (IX+d) | *****V1* | 3 | 19 | ||

| B- | CP A, (IY+d) | A - (IY+d) | *****V1* | 3 | 19 | ||

| INC | B- | INC r | r ← r + 1 | *****V0- | 1 | 4 | |

| B- | INC ur | ur ← ur + 1 | *****V0- | 2 | 8 | ||

| B- | INC (HL) | (HL) ← (HL) + 1 | *****V0- | 1 | 11 | ||

| B- | INC (IX+d) | (IX+d) ← (IX+d) + 1 | *****V0- | 3 | 23 | ||

| B- | INC (IY+d) | (IY+d) ← (IY+d) + 1 | *****V0- | 3 | 23 | ||

| -W | INC r | r ← r + 1 | -------- | 1 | 6 | ||

| -W | INC IX | IX ← IX + 1 | -------- | 2 | 10 | ||

| -W | INC IY | IY ← IY + 1 | -------- | 2 | 10 | ||

| DEC | B- | DEC r | r ← r - 1 | *****V1- | 1 | 4 | |

| B- | DEC ur | ur ← ur - 1 | *****V1- | 2 | 8 | ||

| B- | DEC (HL) | (HL) ← (HL) - 1 | *****V1- | 1 | 11 | ||

| B- | DEC (IX+d) | (IX+d) ← (IX+d) - 1 | *****V1- | 3 | 23 | ||

| B- | DEC (IY+d) | (IY+d) ← (IY+d) - 1 | *****V1- | 3 | 23 | ||

| -W | DEC r | r ← r - 1 | -------- | 1 | 6 | ||

| -W | DEC IX | IX ← IX - 1 | -------- | 2 | 10 | ||

| -W | DEC IY | IY ← IY - 1 | -------- | 2 | 10 | ||

| DAA | B- | DAA | BCD補正 | *****P-* | 1 | 4 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| AND | B- | AND A, r | A ← A and r | ***1*P00 | 1 | 4 | |

| B- | AND A, ur | A ← A and ur | ***1*P00 | 2 | 8 | ||

| B- | AND A, # | A ← A and # | ***1*P00 | 2 | 7 | ||

| B- | AND A, (HL) | A ← A and (HL) | ***1*P00 | 1 | 7 | ||

| B- | AND A, (IX+d) | A ← A and (IX+d) | ***1*P00 | 3 | 19 | ||

| B- | AND A, (IY+d) | A ← A and (IY+d) | ***1*P00 | 3 | 19 | ||

| XOR | B- | XOR A, r | A ← A xor r | ***0*P00 | 1 | 4 | |

| B- | XOR A, ur | A ← A xor ur | ***0*P00 | 2 | 8 | ||

| B- | XOR A, # | A ← A xor # | ***0*P00 | 2 | 7 | ||

| B- | XOR A, (HL) | A ← A xor (HL) | ***0*P00 | 1 | 7 | ||

| B- | XOR A, (IX+d) | A ← A xor (IX+d) | ***0*P00 | 3 | 19 | ||

| B- | XOR A, (IY+d) | A ← A xor (IY+d) | ***0*P00 | 3 | 19 | ||

| OR | B- | OR A, r | A ← A or r | ***0*P00 | 1 | 4 | |

| B- | OR A, ur | A ← A or ur | ***0*P00 | 2 | 8 | ||

| B- | OR A, # | A ← A or # | ***0*P00 | 2 | 7 | ||

| B- | OR A, (HL) | A ← A or (HL) | ***0*P00 | 1 | 7 | ||

| B- | OR A, (IX+d) | A ← A or (IX+d) | ***0*P00 | 3 | 19 | ||

| B- | OR A, (IY+d) | A ← A or (IY+d) | ***0*P00 | 3 | 19 | ||

| CPL | B- | CPL | A ← not A | --*1*-1- | 1 | 4 | |

| NEG | B- | NEG | A ← 0 - A | *****V1* | 2 | 8 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| JP | -- | JP #16 | PC ← #16 | -------- | 3 | 10 | |

| -- | JP cc, #16 | if cc then PC ← #16 | -------- | 3 | 10 | ||

| -- | JP (HL) | PC ← HL | -------- | 1 | 4 | ||

| -- | JP (IX) | PC ← IX | -------- | 2 | 8 | ||

| -- | JP (IY) | PC ← IY | -------- | 2 | 8 | ||

| JR | -- | JR $+2+d | PC ← $+2+d | -------- | 2 | 12 | |

| -- | JR ch, $+2+d | if ch then PC ← $+2+d | -------- | 2 | 12 [true] 7 [false] | ch = C/NC/Z/NZ | |

| DJNZ | -- | DJNZ $+2+d | B ← B-1 if B<>0 then PC ← $+2+d | -------- | 2 | 13 [B<>0] 8 [B=0] | |

| CALL | -- | CALL #16 | SP ← SP - 1 : (SP) ← $+3[15:8] SP ← SP - 1 : (SP) ← $+3[7:0] PC ← #16 | -------- | 3 | 17 | |

| -- | CALL cc,#16 | if cc then CALL #16 | -------- | 3 | 17 [true] 10 [false] | ||

| RET | -- | RET | PC[7:0] ← (SP) : SP ← SP + 1 PC[15:8] ← (SP) : SP ← SP + 1 | -------- | 1 | 10 | |

| -- | RET cc | if cc then RET | -------- | 1 | 11 [true] 5 [false] | ||

| RETI | -- | RET | PC[7:0] ← (SP) : SP ← SP + 1 PC[15:8] ← (SP) : SP ← SP + 1 | -------- | 2 | 14 | |

| RETN | -- | RETN | PC[7:0] ← (SP) : SP ← SP + 1 PC[15:8] ← (SP) : SP ← SP + 1 IFF1 ← IFF2 | -------- | 2 | 14 | |

| RST n | -- | RST n | SP ← SP - 1 : (SP) ← $+1[15:8] SP ← SP - 1 : (SP) ← $+1[7:0] PC ← n | -------- | 1 | 11 | n=$00/$08/$10/$18 n=$20/$28/$30/$38 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

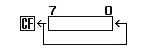

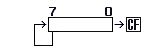

| RLCx | B- | RLCA |  |

--*0*-0* | 1 | 4 | Aレジスタ |

| B- | RLC r | ***0*P0* | 2 | 8 | |||

| B- | RLC (HL) | ***0*P0* | 2 | 15 | |||

| B- | RLC (IX+d) | ***0*P0* | 4 | 23 | |||

| B- | RLC (IY+d) | ***0*P0* | 4 | 23 | |||

| B- | RLC (IX+d),r | r = (IX+d) : RLC : (IX+d) = r | ***0*P0* | 4 | 23 | ||

| B- | RLC (IY+d),r | r = (IY+d) : RLC : (IY+d) = r | ***0*P0* | 4 | 23 | ||

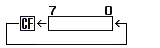

| RLx | B- | RLA |  |

--*0*-0* | 1 | 4 | Aレジスタ |

| B- | RL r | ***0*P0* | 2 | 8 | |||

| B- | RL (HL) | ***0*P0* | 2 | 15 | |||

| B- | RL (IX+d) | ***0*P0* | 4 | 23 | |||

| B- | RL (IY+d) | ***0*P0* | 4 | 23 | |||

| B- | RL (IX+d),r | r = (IX+d) : RL : (IX+d) = r | ***0*P0* | 4 | 23 | ||

| B- | RL (IY+d),r | r = (IY+d) : RL : (IY+d) = r | ***0*P0* | 4 | 23 | ||

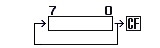

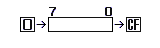

| RRCx | B- | RRCA |  |

--*0*-0* | 1 | 4 | Aレジスタ |

| B- | RRC r | ***0*P0* | 2 | 8 | |||

| B- | RRC (HL) | ***0*P0* | 2 | 15 | |||

| B- | RRC (IX+d) | ***0*P0* | 4 | 23 | |||

| B- | RRC (IY+d) | ***0*P0* | 4 | 23 | |||

| B- | RRC(IX+d),r | r = (IX+d) : RRC : (IX+d) = r | ***0*P0* | 4 | 23 | ||

| B- | RRC (IY+d),r | r = (IY+d) : RRC : (IY+d) = r | ***0*P0* | 4 | 23 | ||

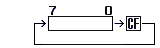

| RRx | B- | RRA |  |

--*0*-0* | 1 | 4 | Aレジスタ |

| B- | RR r | ***0*P0* | 2 | 8 | |||

| B- | RR (HL) | ***0*P0* | 2 | 15 | |||

| B- | RR (IX+d) | ***0*P0* | 4 | 23 | |||

| B- | RR (IY+d) | ***0*P0* | 4 | 23 | |||

| B- | RR (IX+d),r | r = (IX+d) : RR : (IX+d) = r | ***0*P0* | 4 | 23 | ||

| B- | RR (IY+d),r | r = (IY+d) : RR : (IY+d) = r | ***0*P0* | 4 | 23 | ||

| RLD | B- | RLD |  |

***0*P0- | 2 | 18 | |

| RRD | B- | RRD |  |

***0*P0- | 2 | 18 | |

| SLA | B- | SLA r |  |

**-0-P0* | 2 | 8 | |

| B- | SLA (HL) | **-0-P0* | 2 | 15 | |||

| B- | SLA (IX+d) | **-0-P0* | 4 | 23 | |||

| B- | SLA (IY+d) | **-0-P0* | 4 | 23 | |||

| B- | SLA (IX+d),r | r = (IX+d) : SLA : (IX+d) = r | **-0-P0* | 4 | 23 | ||

| B- | SLA (IY+d),r | r = (IY+d) : SLA : (IY+d) = r | **-0-P0* | 4 | 23 | ||

| SLL | B- | SLL r |  |

**-0-P0* | 2 | 8 | |

| B- | SLL (HL) | **-0-P0* | 2 | 15 | |||

| B- | SLL (IX+d) | **-0-P0* | 4 | 23 | |||

| B- | SLL (IY+d) | **-0-P0* | 4 | 23 | |||

| B- | SLL (IX+d),r | r = (IX+d) : SLL : (IX+d) = r | **-0-P0* | 4 | 23 | ||

| B- | SLL (IY+d),r | r = (IY+d) : SLL : (IY+d) = r | **-0-P0* | 4 | 23 | ||

| SRA | B- | SRA r |  |

**-0-P0* | 2 | 8 | |

| B- | SRA (HL) | **-0-P0* | 2 | 15 | |||

| B- | SRA (IX+d) | **-0-P0* | 4 | 23 | |||

| B- | SRA (IY+d) | **-0-P0* | 4 | 23 | |||

| B- | SRA (IX+d),r | r = (IX+d) : SRA : (IX+d) = r | **-0-P0* | 4 | 23 | ||

| B- | SRA (IY+d),r | r = (IY+d) : SRA : (IY+d) = r | **-0-P0* | 4 | 23 | ||

| SRL | B- | SRL r |  |

0*-0-P0* | 2 | 8 | |

| B- | SRL (HL) | 0*-0-P0* | 2 | 15 | |||

| B- | SRL (IX+d) | 0*-0-P0* | 4 | 23 | |||

| B- | SRL (IY+d) | 0*-0-P0* | 4 | 23 | |||

| B- | SRL (IX+d),r | r = (IX+d) : SRL : (IX+d) = r | 0*-0-P0* | 4 | 23 | ||

| B- | SRL (IY+d),r | r = (IY+d) : SRL : (IY+d) = r | 0*-0-P0* | 4 | 23 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| SCF | -- | SCF | CF ← 1 | --*0*-01 | 1 | 4 | |

| CCF | -- | CCF | CF ← not CF | --*C*-0* | 1 | 4 | |

| BIT | B- | BIT #3,r | Z ← r.#3 | ?**1*?0- | 2 | 8 | |

| B- | BIT #3,(HL) | Z ← (HL).#3 | ?**1*?0- | 2 | 12 | ||

| B- | BIT #3,(IX+d) | Z ← (IX+d).#3 | ?**1*?0- | 4 | 20 | ||

| B- | BIT #3,(IY+d) | Z ← (IY+d).#3 | ?**1*?0- | 4 | 20 | ||

| SET | B- | SET #3,r | r.#3 ← 1 | -------- | 2 | 8 | |

| B- | SET #3,(HL) | (HL).#3 ← 1 | -------- | 2 | 15 | ||

| B- | SET #3,(IX+d) | (IX+d).#3 ← 1 | -------- | 4 | 23 | ||

| B- | SET #3,(IY+d) | (IY+d).#3 ← 1 | -------- | 4 | 23 | ||

| B- | SET #3,(IX+d),r | r = (IX+d) : r.#3 = 1 : (IX+d) = r | -------- | 4 | 23 | ||

| B- | SET #3,(IY+d),r | r = (IY+d) : r.#3 = 1 : (IY+d) = r | -------- | 4 | 23 | ||

| RES | B- | RES #3,r | r.#3 ← 0 | -------- | 2 | 8 | |

| B- | RES #3,(HL) | (HL).#3 ← 0 | -------- | 2 | 15 | ||

| B- | RES #3,(IX+d) | (IX+d).#3 ← 0 | -------- | 4 | 23 | ||

| B- | RES #3,(IY+d) | (IY+d).#3 ← 0 | -------- | 4 | 23 | ||

| B- | RES #3,(IX+d),r | r = (IX+d) : r.#3 = 0 : (IX+d) = r | -------- | 4 | 23 | ||

| B- | RES #3,(IY+d),r | r = (IY+d) : r.#3 = 0 : (IY+d) = r | -------- | 4 | 23 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| IN | B- | IN A,(#8) | A ← IO(A#8) | -------- | 2 | 11 | 上位8ビットはA |

| B- | IN r,(C) | r ← IO(BC) | *****P0- | 2 | 12 | 上位8ビットはB | |

| INI | B- | INI | (HL) ← IO(BC) HL ← HL + 1 B ← B - 1 if [B=0] then Z ← 1 else Z ← 0 | ?**?*?1- | 2 | 16 | 上位8ビットはB |

| INIR | B- | INIR | do { INI } while [B<>0] | ?1*?*?1- | 2 | 21 [B<>0] 16 [B=0] | 実行中の割り込み不可 |

| IND | B- | IND | (HL) ← IO(BC) HL ← HL - 1 B ← B - 1 if [B=0] then Z ← 1 else Z ← 0 | ?**?*?1- | 2 | 16 | 上位8ビットはB |

| INDR | B- | INDR | do { IND } while [B<>0] | ?1*?*?1- | 2 | 21 [B<>0] 16 [B=0] | 実行中の割り込み不可 |

| OUT | B- | OUT (#8),A | IO(A#8) ← A | -------- | 2 | 11 | 上位8ビットはA |

| B- | OUT (C),r | IO(BC) ← r | -------- | 2 | 12 | 上位8ビットはB | |

| OUTI | B- | OUTI | IO(BC) ← (HL) HL ← HL + 1 B ← B - 1 if [B=0] then Z ← 1 else Z ← 0 | ?**?*?1- | 2 | 16 | 上位8ビットはB |

| OTIR | B- | OTIR | do { OUTI } while [B<>0] | ?1*?*?1- | 2 | 21 [B<>0] 16 [B=0] | 実行中の割り込み不可 |

| OUTD | B- | OUTD | IO(BC) ← (HL) HL ← HL - 1 B ← B - 1 if [B=0] then Z ← 1 else Z ← 0 | ?**?*?1- | 2 | 16 | 上位8ビットはB |

| OTDR | B- | OTDR | do { OUTD } while [B<>0] | ?1*?*?1- | 2 | 21 [B<>0] 16 [B=0] | 実行中の割り込み不可 |

| 命令群 | サイズ | ニーモニック | 機能 | SZXHXPNC | 命令長 | ステート | 補足 |

| NOP | -- | NOP | 何もしない | -------- | 1 | 4 | |

| HALT | -- | HALT | CPU停止 | -------- | 1 | 4 | |

| DI | -- | DI | IFF ← 0 | -------- | 1 | 4 | |

| EI | -- | EI | IFF ← 1 | -------- | 1 | 4 | |

| IM | -- | IM n | -------- | 2 | 8 | n = 0/1/2 |

命令コードマップ

色の説明

1. 文字・背景色

| 実装済み |

| 未実装 |

| 未定義命令 |

| 未定義命令・未実装 |

命令コード

| H/L | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 0 | NOP | LD BC,# |

LD (BC),A |

INC BC |

INC B |

DEC B |

LD B,# |

RLCA | EX AF,AF' |

ADD HL,BC |

LD A,(BC) |

DEC BC |

INC C |

DEC C |

LD C,# |

RRCA |

| 1 | DJNZ PC+d |

LD DE,# |

LD (DE),A |

INC DE |

INC D |

DEC D |

LD D,# |

RLA | JR PC+d |

ADD HL,DE |

LD A,(DE) |

DEC DE |

INC E |

DEC E |

LD E,# |

RRA |

| 2 | JR nz,PC+d |

LD HL,# |

LD (#16),HL |

INC HL |

INC H |

DEC H |

LD H,# |

DAA | JR z,PC+d |

ADD HL,HL |

LD HL,(#16) |

DEC HL |

INC L |

DEC L |

LD L,# |

CPL |

| 3 | JR nc,PC+d |

LD SP,# |

LD (#16),A |

INC SP |

INC (HL) |

DEC (HL) |

LD (HL),# |

SCF | JR c,PC+d |

ADD HL,SP |

LD A,(#16) |

DEC SP |

INC A |

DEC A |

LD A,# |

CCF |

| 4 | LD B,B |

LD B,C |

LD B,D |

LD B,E |

LD B,H |

LD B,L |

LD B,(HL) |

LD B,A |

LD C,B |

LD C,C |

LD C,D |

LD C,E |

LD C,H |

LD C,L |

LD C,(HL) |

LD C,A |

| 5 | LD D,B |

LD D,C |

LD D,D |

LD D,E |

LD D,H |

LD D,L |

LD D,(HL) |

LD D,A |

LD E,B |

LD E,C |

LD E,D |

LD E,E |

LD E,H |

LD E,L |

LD E,(HL) |

LD E,A |

| 6 | LD H,B |

LD H,C |

LD H,D |

LD H,E |

LD H,H |

LD H,L |

LD H,(HL) |

LD H,A |

LD L,B |

LD L,C |

LD L,D |

LD L,E |

LD L,H |

LD L,L |

LD L,(HL) |

LD L,A |

| 7 | LD (HL),B |

LD (HL),C |

LD (HL),D |

LD (HL),E |

LD (HL),H |

LD (HL),L |

HALT | LD (HL),A |

LD A,B |

LD A,C |

LD A,D |

LD A,E |

LD A,H |

LD A,L |

LD A,(HL) |

LD A,A |

| 8 | ADD A,B |

ADD A,C |

ADD A,D |

ADD A,E |

ADD A,H |

ADD A,L |

ADD A,(HL) |

ADD A,A |

ADC A,B |

ADC A,C |

ADC A,D |

ADC A,E |

ADC A,H |

ADC A,L |

ADC A,(HL) |

ADC A,A |

| 9 | SUB A,B |

SUB A,C |

SUB A,D |

SUB A,E |

SUB A,H |

SUB A,L |

SUB A,(HL) |

SUB A,A |

SBC A,B |

SBC A,C |

SBC A,D |

SBC A,E |

SBC A,H |

SBC A,L |

SBC A,(HL) |

SBC A,A |

| A | AND A,B |

AND A,C |

AND A,D |

AND A,E |

AND A,H |

AND A,L |

AND A,(HL) |

AND A,A |

XOR A,B |

XOR A,C |

XOR A,D |

XOR A,E |

XOR A,H |

XOR A,L |

XOR A,(HL) |

XOR A,A |

| B | OR A,B |

OR A,C |

OR A,D |

OR A,E |

OR A,H |

OR A,L |

OR A,(HL) |

OR A,A |

CP A,B |

CP A,C |

CP A,D |

CP A,E |

CP A,H |

CP A,L |

CP A,(HL) |

CP A,A |

| C | RET nz |

POP BC |

JP nz,#16 |

JP #16 |

CALL nz,#16 |

PUSH BC |

ADD A,# |

RST 00h |

RET z |

RET | JP z,#16 |

$CB | CALL z,#16 |

CALL #16 |

ADC A,# |

RST 08h |

| D | RET nc |

POP DE |

JP nc,#16 |

OUT (#8),A |

CALL nc,#16 |

PUSH DE |

SUB A,# |

RST 10h |

RET c |

EXX | JP c,#16 |

IN A,(#8) |

CALL c,#16 |

$DD | SBC A,# |

RST 18h |

| E | RET po |

POP HL |

JP po,#16 |

EX (SP),HL |

CALL po,#16 |

PUSH HL |

AND A,# |

RST 20h |

RET pe |

JP (HL) |

JP pe,#16 |

EX DE,HL |

CALL pe,#16 |

$ED | XOR A,# |

RST 28h |

| F | RET p |

POP AF |

JP p,#16 |

DI | CALL p,#16 |

PUSH AF |

OR A,# |

RST 30h |

RET m |

LD SP,HL |

JP m,#16 |

EI | CALL m,#16 |

$FD | CP A,# |

RST 38h |

| H/L | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 0 | RLC B |

RLC C |

RLC D |

RLC E |

RLC H |

RLC L |

RLC (HL) |

RLC A |

RRC B |

RRC C |

RRC D |

RRC E |

RRC H |

RRC L |

RRC (HL) |

RRC A |

| 1 | RL B |

RL C |

RL D |

RL E |

RL H |

RL L |

RL (HL) |

RL A |

RR B |

RR C |

RR D |

RR E |

RR H |

RR L |

RR (HL) |

RR A |

| 2 | SLA B |

SLA C |

SLA D |

SLA E |

SLA H |

SLA L |

SLA (HL) |

SLA A |

SRA B |

SRA C |

SRA D |

SRA E |

SRA H |

SRA L |

SRA (HL) |

SRA A |

| 3 | SLL B |

SLL C |

SLL D |

SLL E |

SLL H |

SLL L |

SLL (HL) |

SLL A |

SRL B |

SRL C |

SRL D |

SRL E |

SRL H |

SRL L |

SRL (HL) |

SRL A |

| 4 | BIT 0,B |

BIT 0,C |

BIT 0,D |

BIT 0,E |

BIT 0,H |

BIT 0,L |

BIT 0,(HL) |

BIT 0,A |

BIT 1,B |

BIT 1,C |

BIT 1,D |

BIT 1,E |

BIT 1,H |

BIT 1,L |

BIT 1,(HL) |

BIT 1,A |

| 5 | BIT 2,B |

BIT 2,C |

BIT 2,D |

BIT 2,E |

BIT 2,H |

BIT 2,L |

BIT 2,(HL) |

BIT 2,A |

BIT 3,B |

BIT 3,C |

BIT 3,D |

BIT 3,E |

BIT 3,H |

BIT 3,L |

BIT 3,(HL) |

BIT 3,A |

| 6 | BIT 4,B |

BIT 4,C |

BIT 4,D |

BIT 4,E |

BIT 4,H |

BIT 4,L |

BIT 4,(HL) |

BIT 4,A |

BIT 5,B |

BIT 5,C |

BIT 5,D |

BIT 5,E |

BIT 5,H |

BIT 5,L |

BIT 5,(HL) |

BIT 5,A |

| 7 | BIT 6,B |

BIT 6,C |

BIT 6,D |

BIT 6,E |

BIT 6,H |

BIT 6,L |

BIT 6,(HL) |

BIT 6,A |

BIT 7,B |

BIT 7,C |

BIT 7,D |

BIT 7,E |

BIT 7,H |

BIT 7,L |

BIT 7,(HL) |

BIT 7,A |

| 8 | RES 0,B |

RES 0,C |

RES 0,D |

RES 0,E |

RES 0,H |

RES 0,L |

RES 0,(HL) |

RES 0,A |

RES 1,B |

RES 1,C |

RES 1,D |

RES 1,E |

RES 1,H |

RES 1,L |

RES 1,(HL) |

RES 1,A |

| 9 | RES 2,B |

RES 2,C |

RES 2,D |

RES 2,E |

RES 2,H |

RES 2,L |

RES 2,(HL) |

RES 2,A |

RES 3,B |

RES 3,C |

RES 3,D |

RES 3,E |

RES 3,H |

RES 3,L |

RES 3,(HL) |

RES 3,A |

| A | RES 4,B |

RES 4,C |

RES 4,D |

RES 4,E |

RES 4,H |

RES 4,L |

RES 4,(HL) |

RES 4,A |

RES 5,B |

RES 5,C |

RES 5,D |

RES 5,E |

RES 5,H |

RES 5,L |

RES 5,(HL) |

RES 5,A |

| B | RES 6,B |

RES 6,C |

RES 6,D |

RES 6,E |

RES 6,H |

RES 6,L |

RES 6,(HL) |

RES 6,A |

RES 7,B |

RES 7,C |

RES 7,D |

RES 7,E |

RES 7,H |

RES 7,L |

RES 7,(HL) |

RES 7,A |

| C | SET 0,B |

SET 0,C |

SET 0,D |

SET 0,E |

SET 0,H |

SET 0,L |

SET 0,(HL) |

SET 0,A |

SET 1,B |

SET 1,C |

SET 1,D |

SET 1,E |

SET 1,H |

SET 1,L |

SET 1,(HL) |

SET 1,A |

| D | SET 2,B |

SET 2,C |

SET 2,D |

SET 2,E |

SET 2,H |

SET 2,L |

SET 2,(HL) |

SET 2,A |

SET 3,B |

SET 3,C |

SET 3,D |

SET 3,E |

SET 3,H |

SET 3,L |

SET 3,(HL) |

SET 3,A |

| E | SET 4,B |

SET 4,C |

SET 4,D |

SET 4,E |

SET 4,H |

SET 4,L |

SET 4,(HL) |

SET 4,A |

SET 5,B |

SET 5,C |

SET 5,D |

SET 5,E |

SET 5,H |

SET 5,L |

SET 5,(HL) |

SET 5,A |

| F | SET 6,B |

SET 6,C |

SET 6,D |

SET 6,E |

SET 6,H |

SET 6,L |

SET 6,(HL) |

SET 6,A |

SET 7,B |

SET 7,C |

SET 7,D |

SET 7,E |

SET 7,H |

SET 7,L |

SET 7,(HL) |

SET 7,A |

| H/L | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 0 | ||||||||||||||||

| 1 | ||||||||||||||||

| 2 | ||||||||||||||||

| 3 | ||||||||||||||||

| 4 | IN B,(C) |

OUT (C),B |

SBC HL,BC |

LD (#16),BC |

NEG | RETN | IM 0 |

LD I,A |

IN C,(C) |

OUT (C),C |

ADC HL,BC |

LD BC,(#16) |

NEG | RETI | IM 0 |

LD R,A |

| 5 | IN D,(C) |

OUT (C),D |

SBC HL,DE |

LD (#16),DE |

NEG | RETN | IM 1 |

LD A,I |

IN E,(C) |

OUT (C),E |

ADC HL,DE |

LD DE,(#16) |

NEG | RETN | IM 2 |

LD A,R |

| 6 | IN H,(C) |

OUT (C),H |

SBC HL,HL |

LD (#16),HL | NEG | RETN | IM 0 |

RRD | IN L,(C) |

OUT (C),L |

ADC HL,HL |

LD HL,(#16) |

NEG | RETN | IM 0 |

RLD |

| 7 | IN F,(C) |

OUT (C),0 |

SBC HL,SP |

LD (#16),SP |

NEG | RETN | IM 1 |

IN A,(C) |

OUT (C),A |

ADC HL,SP |

LD SP,(#16) |

NEG | RETN | IM 2 |

||

| 8 | ||||||||||||||||

| 9 | ||||||||||||||||

| A | LDI | CPI | INI | OUTI | LDD | CPD | IND | OUTD | ||||||||

| B | LDIR | CPIR | INIR | OTIR | LDDR | CPDR | INDR | OTDR | ||||||||

| C | ||||||||||||||||

| D | ||||||||||||||||

| E | ||||||||||||||||

| F |

| H/L | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 0 | ADD IX,BC |

|||||||||||||||

| 1 | ADD IX,DE |

|||||||||||||||

| 2 | LD IX,# |

LD (#16),IX |

INC IX |

INC IXH |

DEC IXH |

LD IXH,# |

ADD IX,IX |

LD IX,(#16) |

DEC IX |

INC IXL |

DEC IXL |

LD IXL,# |

||||

| 3 | INC (IX+d) |

DEC (IX+d) |

LD (IX+d),# |

ADD IX,SP |

||||||||||||

| 4 | LD B,IXH |

LD B,IXL |

LD B,(IX+d) |

LD C,IXH |

LD C,IXL |

LD C,(IX+d) |

||||||||||

| 5 | LD D,IXH |

LD D,IXL |

LD D,(IX+d) |

LD E,IXH |

LD E,IXL |

LD E,(IX+d) |

||||||||||

| 6 | LD IXH,B |

LD IXH,C |

LD IXH,D |

LD IXH,E |

LD IXH,IXH |

LD IXH,IXL |

LD H,(IX+d) |

LD IXH,A |

LD IXL,B |

LD IXL,C |

LD IXL,D |

LD IXL,E |

LD IXL,IXH |

LD IXL,IXL |

LD L,(IX+d) |

LD IXL,A |

| 7 | LD (IX+d),B |

LD (IX+d),C |

LD (IX+d),D |

LD (IX+d),E |

LD (IX+d),H |

LD (IX+d),L |

LD (IX+d),A |

LD A,IXH |

LD A,IXL |

LD A,(IX+d) |

||||||

| 8 | ADD A,IXH |

ADD A,IXL |

ADD A,(IX+d) |

ADC A,IXH |

ADC A,IXL |

ADC A,(IX+d) |

||||||||||

| 9 | SUB A,IXH |

SUB A,IXL |

SUB A,(IX+d) |

SBC A,IXH |

SBC A,IXL |

SBC A,(IX+d) |

||||||||||

| A | AND IXH |

AND IXL |

AND A,(IX+d) |

XOR IXH |

XOR IXL |

XOR A,(IX+d) |

||||||||||

| B | OR IXH |

OR IXL |

OR A,(IX+d) |

CP IXH |

CP IXL |

CP A,(IX+d) |

||||||||||

| C | $CB | |||||||||||||||

| D | ||||||||||||||||

| E | POP IX |

EX (SP),IX |

PUSH IX |

JP (IX) |

||||||||||||

| F | LD SP,IX |

※上記はオペコードが$DD時、$FDの時はIXがIY

| H/L | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | A | B | C | D | E | F |

| 0 | RLC (IX+d),B |

RLC (IX+d),C |

RLC (IX+d),D |

RLC (IX+d),E |

RLC (IX+d),H |

RLC (IX+d),L |

RLC (IX+d) |

RRC (IX+d),A |

RRC (IX+d),B |

RRC (IX+d),C |

RRC (IX+d),D |

RRC (IX+d),E |

RRC (IX+d),H |

RRC (IX+d),L |

RRC (IX+d) |

RRC (IX+d),A |

| 1 | RL (IX+d),B |

RL (IX+d),C |

RL (IX+d),D |

RL (IX+d),E |

RL (IX+d),H |

RL (IX+d),L |

RL (IX+d) |

RL (IX+d),A |

RR (IX+d),B |

RR (IX+d),C |

RR (IX+d),D |

RR (IX+d),E |

RR (IX+d),H |

RR (IX+d),L |

RR (IX+d) |

RR (IX+d),A |

| 2 | SLA (IX+d),B |

SLA (IX+d),C |

SLA (IX+d),D |

SLA (IX+d),E |

SLA (IX+d),H |

SLA (IX+d),L |

SLA (IX+d) |

SLA (IX+d),A |

SRA (IX+d),B |

SRA (IX+d),C |

SRA (IX+d),D |

SRA (IX+d),E |

SRA (IX+d),H |

SRA (IX+d),L |

SRA (IX+d) |

SRA (IX+d),A |

| 3 | SLL (IX+d),B |

SLL (IX+d),C |

SLL (IX+d),D |

SLL (IX+d),E |

SLL (IX+d),H |

SLL (IX+d),L |

SLL (IX+d) |

SLL (IX+d),A |

SRL (IX+d),B |

SRL (IX+d),C |

SRL (IX+d),D |

SRL (IX+d),E |

SRL (IX+d),H |

SRL (IX+d),L |

SRL (IX+d) |

SRL (IX+d),A |

| 4 | BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 0,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

BIT 1,(IX+d) |

| 5 | BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 2,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

BIT 3,(IX+d) |

| 6 | BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 4,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

BIT 5,(IX+d) |

| 7 | BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 6,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

BIT 7,(IX+d) |

| 8 | RES 0,(IX+d),B |

RES 0,(IX+d),C |

RES 0,(IX+d),D |

RES 0,(IX+d),E |

RES 0,(IX+d),H |

RES 0,(IX+d),L |

RES 0,(IX+d) |

RES 0,(IX+d),A |

RES 1,(IX+d),B |

RES 1,(IX+d),C |

RES 1,(IX+d),D |

RES 1,(IX+d),E |

RES 1,(IX+d),H |

RES 1,(IX+d),L |

RES 1,(IX+d) |

RES 1,(IX+d),A |

| 9 | RES 2,(IX+d),B |

RES 2,(IX+d),C |

RES 2,(IX+d),D |

RES 2,(IX+d),E |

RES 2,(IX+d),H |

RES 2,(IX+d),L |

RES 2,(IX+d) |

RES 2,(IX+d),A |

RES 3,(IX+d),B |

RES 3,(IX+d),C |

RES 3,(IX+d),D |

RES 3,(IX+d),E |

RES 3,(IX+d),H |

RES 3,(IX+d),L |

RES 3,(IX+d) |

RES 3,(IX+d),A |

| A | RES 4,(IX+d),B |

RES 4,(IX+d),C |

RES 4,(IX+d),D |

RES 4,(IX+d),E |

RES 4,(IX+d),H |

RES 4,(IX+d),L |

RES 4,(IX+d) |

RES 4,(IX+d),A |

RES 5,(IX+d),B |

RES 5,(IX+d),C |

RES 5,(IX+d),D |

RES 5,(IX+d),E |

RES 5,(IX+d),H |

RES 5,(IX+d),L |

RES 5,(IX+d) |

RES 5,(IX+d),A |

| B | RES 6,(IX+d),B |

RES 6,(IX+d),C |

RES 6,(IX+d),D |

RES 6,(IX+d),E |

RES 6,(IX+d),H |

RES 6,(IX+d),L |

RES 6,(IX+d) |

RES 6,(IX+d),A |

RES 7,(IX+d),B |

RES 7,(IX+d),C |

RES 7,(IX+d),D |

RES 7,(IX+d),E |

RES 7,(IX+d),H |

RES 7,(IX+d),L |

RES 7,(IX+d) |

RES 7,(IX+d),A |

| C | SET 0,(IX+d),A |

SET 0,(IX+d),B |

SET 0,(IX+d),C |

SET 0,(IX+d),D |

SET 0,(IX+d),E |

SET 0,(IX+d),L |

SET 0,(IX+d) |

SET 0,(IX+d),A |

SET 1,(IX+d),B |

SET 1,(IX+d),C |

SET 1,(IX+d),D |

SET 1,(IX+d),E |

SET 1,(IX+d),H |

SET 1,(IX+d),L |

SET 1,(IX+d) |

SET 1,(IX+d),A |

| D | SET 2,(IX+d),A |

SET 2,(IX+d),B |

SET 2,(IX+d),C |

SET 2,(IX+d),D |

SET 2,(IX+d),E |

SET 2,(IX+d),L |

SET 2,(IX+d) |

SET 2,(IX+d),A |

SET 3,(IX+d),B |

SET 3,(IX+d),C |

SET 3,(IX+d),D |

SET 3,(IX+d),E |

SET 3,(IX+d),H |

SET 3,(IX+d),L |

SET 3,(IX+d) |

SET 3,(IX+d),A |

| E | SET 4,(IX+d),A |

SET 4,(IX+d),B |

SET 4,(IX+d),C |

SET 4,(IX+d),D |

SET 4,(IX+d),E |

SET 4,(IX+d),L |

SET 4,(IX+d) |

SET 4,(IX+d),A |

SET 5,(IX+d),B |

SET 5,(IX+d),C |

SET 5,(IX+d),D |

SET 5,(IX+d),E |

SET 5,(IX+d),H |

SET 5,(IX+d),L |

SET 5,(IX+d) |

SET 5,(IX+d),A |

| F | SET 6,(IX+d),A |

SET 6,(IX+d),B |

SET 6,(IX+d),C |

SET 6,(IX+d),D |

SET 6,(IX+d),E |

SET 6,(IX+d),L |

SET 6,(IX+d) |

SET 6,(IX+d),A |

SET 7,(IX+d),B |

SET 7,(IX+d),C |

SET 7,(IX+d),D |

SET 7,(IX+d),E |

SET 7,(IX+d),H |

SET 7,(IX+d),L |

SET 7,(IX+d) |

SET 7,(IX+d),A |

※上記はオペコードの1バイト目が$DD時、$FDの時はIXがIY